# NON-VOLATILE RAM GR881 (8k X 8)

# T& ELECTRONIC SOLUTIONS

# Description

The GR881 is a 8192 word by 8 bits (8k x 8) nonvolatile, advanced silicon gate, CMOS 70nS Static RAM IC with a high operational industrial temperature range. Memory contents are retained by the use of an internal, highly reliable, lithium power cell. Without any external power, the data retention is typically greater than ten years.

The pin-out of the device conforms to the JEDEC standards and is fully compatible with normal Static RAM. The power down circuit is fully automatic and is referenced at 4.5Vdc. At this point it is write-protected by an internal inhibit function for data protection and the memory contents are retained by the internal lithium cell.

Essential for data integrity, power down is very fast, less than 15µS from 5V to 0Vdc, faster than system power failure conditions.

# Application

When powered down, the device is transportable and the data contained can be moved from system to system making it ideal for program development, data collection in data-loggers, program changes in process control systems, automation and user-definable lookup tables etc.

# **Absolute Ratings**

| SYMBOL  | MIN  | MAX     | UNITS |

|---------|------|---------|-------|

| Vdd     | -0.3 | 7.0     | Vdc   |

| Vin/out | -0.3 | Vdd+0.3 | Vdc   |

| Temp    | -40  | +85     | °C    |

# **Operating Conditions**

| SYMBOL                 | MIN   | TYP. | MAX     | UNITS |

|------------------------|-------|------|---------|-------|

| Vdd                    | +4.75 | +5.0 | +5.5    | Vdc   |

| Vin(1)                 | +2.2  |      | Vdd+0.3 | Vdc   |

| Vin(0)                 | -0.3  |      | +0.8    | Vdc   |

| lin<br>(any other pin) | -1.0  |      | +1.0    | μΑ    |

| Vout(1)<br>(lout=-1mA) | +2.4  |      |         | Vdc   |

| Vout(0)<br>(lout=+2mA) |       |      | +0.4    | Vdc   |

| Idd(active)            |       | 30   |         | mA    |

| Idd(deselected)        |       | 1.0  |         | mA    |

| Tcycle                 |       |      | 70      | nS    |

| Cin(any pin)           |       | 10   |         | pF    |

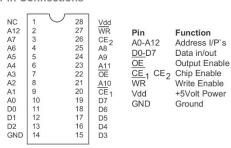

# **Pin Connections**

# GREENWICH INSTRUMENTS GR881 NON-VOLATILE RAM (8K X 8)

#### **Operating Mode**

| CE | ŌĒ    | WR | MODE OUTPUT |             | ldd     |

|----|-------|----|-------------|-------------|---------|

| Н  | Χ     | Χ  | Unsel. Hi-Z |             | Standby |

| L  | Η     | Н  | Unsel.      | Unsel. Hi-Z |         |

| L  | L     | Н  | Read        | Read Dout   |         |

| L  | L X L |    | Write       | Din         | Active  |

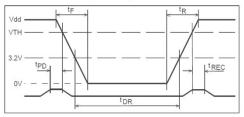

# **Data Retention Operating Conditions**

| SYM  | PARAMETER                          | MIN | TYP. | MAX | UNITS |

|------|------------------------------------|-----|------|-----|-------|

| Vdd  | Operating supply voltage           |     | 5.0  | 5.5 | Vdc   |

| Vтн  | Data retention voltage             |     | 4.5  |     | Vdc   |

| tr   | V <sub>dd</sub> slew to 0V         | 15  |      |     | μS    |

| tr   | V <sub>dd</sub> slew from 0V to 5V | 15  |      |     | μS    |

| trec | CE to O/P valid from power up      |     |      | 15  | μS    |

| tor  | Data retention time                |     | 10   |     | Yrs.  |

| tpD  | CE at Vin(1) before power down     | 0   |      |     | μS    |

# Please note:

- 1. WR must be high during address transitions

- 2. A write occurs during the overlap of active CE and a low WR 3. CE = CE1 and CE2  $\,$

- 4. WR is high for a read cycle

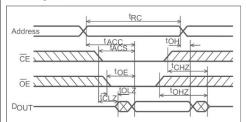

# Read Cycle

| SYM  | PARAMETER            |    | MAX | UNITS |

|------|----------------------|----|-----|-------|

| trc  | Read cycle time      | 70 | 7   | nS    |

| tacc | Access time          |    | 70  | nS    |

| tacs | CE to output valid   |    | 70  | nS    |

| toe  | OE to output valid   |    | 35  | nS    |

| tcLZ | CE to output active  | 10 |     | nS    |

| torz | OE to output active  | 10 |     | nS    |

| tон  | Output hold time     | 10 |     | nS    |

| tснz | CE to output disable |    | 25  | nS    |

| tонz | OE to output disable |    | 25  | nS    |

|      |                      |    |     |       |

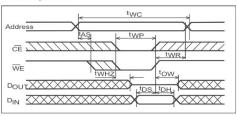

# Write Cycle 1

7.5

|      |                       | _  |     |       |

|------|-----------------------|----|-----|-------|

| SYM  | PARAMETER             |    | MAX | UNITS |

| twc  | Write cycle time      | 70 |     | nS    |

| twp  | Write pulse width     | 50 |     | nS    |

| tas  | Address setup time    | 0  |     | nS    |

| twr  | Write recovery time   | 10 |     | nS    |

| twnz | WR to output disable  |    | 20  | nS    |

| tow  | Output active from WR | 5  |     | nS    |

| tos  | Data setup time       | 30 |     | nS    |

| tон  | Data HOLD TIME        |    |     | nS    |

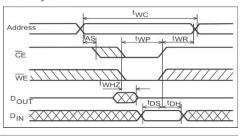

# Write Cycle 2

TecSys by T&O Electronic Solutions GmbH Tiefenbachstr. 5 83734 Hausham Germany

Tel: +49 8026 92 862 - 0 Email: sales@tecsys.de https://shop.tecsys.de Do not dispose of non-volatile memory devices by incineration, crushing or landfill; devices can be returned, carriage paid, to Cephos Relays Limited for disposal